# Teststrukturen zur effizienten produktionsbegleitenden Defektdiagnose und -analyse

Hess, Christopher, Institut für Rechnerentwurf und Fehlertoleranz (Prof. Dr. D. Schmid), Universität Karlsruhe, Zirkel 2, W-7500 Karlsruhe 1

# 1 Kurzfassung

Für Defekte, die innerhalb von Verdrahtungsebenen (z. B. Polysilizium-Layer und Aluminium-Layer) auftreten können, wurden Teststrukturen entwickelt, welche diese Defekte innerhalb einer großen Fläche zuverlässig diagnostizieren. Dabei wird die Anschlußpunktkonfiguration üblicher Standard-Chips verwendet sowie die dabei übliche Meßmethode (Digitaltester) eingesetzt. Trotz der dadurch beschränkten Anzahl der Anschlüsse kann durch den Einsatz neu entwickelter Verfahren die gesamte Fläche des Test-Chips in eine große Anzahl wohlunterscheidbarer Karrees unterteilt werden, ohne daß dazu zusätzliche aktive Bauelemente erforderlich sind. Die Anzahl der Karrees wächst dabei quadratisch mit der Anzahl der zur Verfügung stehenden Anschlußpunkte. Schlagworte: Teststruktur, Defekt, Fehler, Defektdiagnose, Defektstatistik, Permutationsverfahren

### 2 Einleitung

In hochintegrierten Schaltungen können herstellungsbedingt *Defekte* und daraus resultierend *Fehler* auftreten. Als *Defekte* werden vom Entwurf abweichende geometrische oder chemische Veränderungen innerhalb der Layout-Ebene bezeichnet. Veränderungen der elektrischen Parameter wie Spannung, Strom und Widerstand werden als *Fehler* bezeichnet, sofern durch sie die entworfene beabsichtigte Schaltungsfunktion verändert wird. Bereits seit längerer Zeit werden im Bereich der Testmustergenerierung Untersuchungen vorangetrieben, welche die tatsächlich in einem Herstellungsprozeß auftretenden Probleme in Fehlermodellen genauer berücksichtigen (Induktive Fehleranalyse [FeSh88]; testfreundliche Funktionsrepräsentation [Ferr85], [SpSt92]; Testmusterreduktion unter Berücksichtigung von Fehlerwahrscheinlichkeiten [Spie93]). Ähnliches gilt auch für die Ausbeutevorhersage, die Erstellung neuer Entwurfsregeln (Design Rules) sowie die Optimierung von Herstellungsprozeßschritten [Stap84].

In diesem Zusammenhang werden zahlreiche statistisch signifikante Angaben über den momentanen Zustand des Prozesses benötigt. Unter Prozeβzustand soll hier die augenblickliche Häufigkeitsverteilung von Angaben wie Art, Größe, Form, Ursache usw. der auftretenden Defekte sowie die dafür verantwortlichen Prozeßschritte verstanden werden. Dazu werden innerhalb des Prozesses geometrische Gebilde (Defektmonitore bzw. Test-strukturen) gefertigt, die bisher jedoch einerseits nur über eine sehr begrenzte defektsensitive Fläche verfügen, innerhalb derer Defekte überhaupt erkennbar sind und andererseits bestimmte Defektparameter wie beispielsweise die Defektform und Ursache, überhaupt nicht diagnostizieren [Bueh83], [LYWM86], [BCKJ91]. Diese Teststrukturen werden auf Test-Chips in zumeist wenigen Chargen innerhalb einer Fabrikationslinie hergestellt und anschließend zeitaufwendigen analogen Testprozeduren unterzogen. Diese analogen Testverfahren behindern jedoch die parallele Auswertung von Standard-Chips und Test-Chips, die notwendig wäre, um die zwischen den Chargen auftretenden starken Schwankungen der einzelnen Parameter berücksichtigen zu können. Nur wenn Test-Chips gleichzeitig mit Standard-Chips (d. h. auf demselben Wafer, bzw. innerhalb derselben Charge) produktionsbegleitend eingesetzt werden, kann man mit nur geringem Mehraufwand laufend Angaben über den momentanen Zustand des Prozesses erhalten, die repräsentativ bezüglich eines gesamten Herstellungsprozesses sind.

Im Rahmen eines Forschungsprojekts am Institut für Rechnerentwurf und Fehlertoleranz der Universität Karlsruhe werden neue *Teststrukturen* entwickelt, mit deren Hilfe die in Prozessen zur Herstellung digitaler Schaltungen auftretenden Defekte *effizient diagnostiziert* und *analysiert* werden können, um so eine ständige produktionsbegleitende Prozeßkontrolle zu ermöglichen. Dabei wird unter *Diagnose* die Erkennung, Lokalisierung und Identifizierung der Defekte verstanden. Die *Analyse* beinhaltet einerseits die Zusammenstellung von Defektparametern wie Art, Größe, Form und Ursache sowie andererseits statistische Angaben über diese Parameter wie Defektdichten und Cluster-Bilder (*Defektstatistik*). *Effizient* bedeutet in diesem Zusammenhang, daß mit möglichst geringem zusätzlichem Aufwand diese Angaben erstellt werden sollen, wozu beispielsweise der Einsatz bereits vorhandener Meßapparaturen beiträgt. Im folgenden Abschnitt wird auf die Methoden zur Defektdiagnose eingegangen. In Abschnitt 4 wird ein Verfahren zur Defektlokalisierung vorgestellt. Abschnitt 5 beschreibt die Teststrukturen und Abschnitt 6 gibt einen Überblick über die Datenanalyse dieser Strukturen.

### 3 Methoden der Defektdiagnose

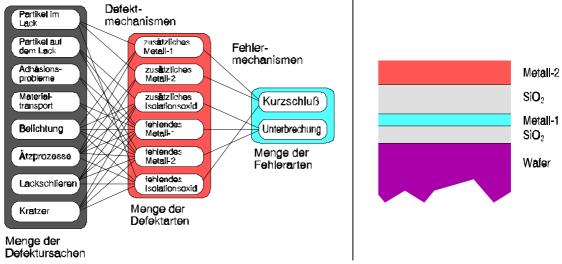

Im folgenden wird nur auf topologische Defekte in Form eines zusätzlichen Materialauftrags (extra material defect EMD) oder in Form von fehlendem Material (missing material defect MMD) eingegangen. Je nach dem, ob das Material leitend oder isolierend ist, kann ein solcher Defekt zu einem Kurzschluß oder zu einer Unterbrechung führen. **Abbildung 1** zeigt links die Abhängigkeit zwischen Defekten, ihren möglichen Ursachen sowie den Folgefehlern einer Materialkonfiguration "METALL-1 - ISOLATIONSOXID - METALL-2", die häufig für die Verdrahtungsebenen in hochintegrierten Schaltungen verwendet wird (Abb. 1 rechts).

Abb. 1: Defektrelation (links) und Materiallagenkonfiguration (rechts)

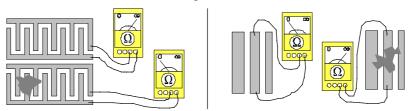

Kurzschlüsse und Unterbrechungen können erkannt werden, indem man überprüft, ob zwischen zwei Anschlußpunkten eine leitende Verbindung (Stromfluß) besteht oder nicht (kein Stromfluß) (vgl. **Abb. 2**). Dazu kann entweder ein analoges Ohm-Meter eingesetzt werden oder aber ein Digitaltester verwendet werden, wenn man die binäre Information ("0" oder "1") der Angabe "Verbindung vorhanden" ("1") bzw. "Verbindung nicht vorhanden" ("0") zuordnet. Dies ist durch die Justierung der Eingangsspannung, der Schwellenspannung zwischen "0" und "1" sowie der verwendeten Meßfrequenz erreichbar [HeWe92], [HeWe92a].

Abb. 2: Defektdiagnose bei Kurzschlüssen (links) und Defektdiagnose bei Unterbrechungen (rechts)

Um Kurzschlüsse zu erkennen, werden Teststrukturen eingesetzt, die aus möglichst vielen elektrisch isolierten Bahnen mit verschiedenen Spannungen bestehen, die im Falle eines Kurzschlusses zu einer gemeinsamen Spannung "verschmelzen" (mehrere Spannungen → eine Spannung, Abb. 2 links). Unterbrechungen werden mit Teststrukturen erkannt, deren Bahnen zwischen mehreren Anschlüssen verlegt sind und somit auf gleicher Spannung liegen, die im Falle einer Unterbrechung in unterscheidbare Spannungen "aufgespalten" wird, da die Anschlüsse der Bahnen dann voneinander isoliert sind (ein Spannung → mehrere Spannung, Abb. 2 rechts).

Welcher konkrete Defekt zu einem so erkannten Fehler geführt hat und welche Ursache innerhalb des Prozesses für den Defekt verantwortlich ist, kann nur durch zusätzliche optische Untersuchungen bestimmt werden. Abbildungen der Defekte sind auch bei der Feststellung der kausalen Zusammenhänge, wie einerseits Defekte zu Fehlern führen (*Fehlermechanismus*, vgl. Abb. 1) und andererseits prozeßbedingte Ursachen Defekte hervorrufen (*Defektmechanismus*, vgl. Abb. 1), sehr hilfreich. Bestimmte Defektparameter wie Größe und Form lassen sich ebenfalls nur mit optischen Meßgeräten präzise ermitteln. Um optische Untersuchungen zu beschleunigen, ist eine Defektlokalisierung an Hand der Daten des elektrischen Tests unumgänglich. Der nächste Abschnitt behandelt daher ein neu entwickeltes Verfahren, welches die Lokalisierung innerhalb einer großen defektsensitiven Fläche ermöglicht, obwohl die Anzahl der nach außen geführten Anschlüsse vergleichsweise gering ist.

### 4 Permutationsverfahren zur Defektlokalisierung

Geht man davon aus, daß je Anschlußpunkt prinzipiell eine (unterscheidbare) Spannung abgegriffen wird, so kann jede Teststruktur in einen Graphen abgebildet werden. Dabei entsprechen die Anschlußpunkte den Knoten und die möglichen elektrisch leitenden Verbindungen zwischen den Anschlußpunkten den Kanten des Graphen. Diese Kanten können zur Diagnose von Unterbrechungen beabsichtigt sein oder durch Kurzschlüsse unbeabsichtigt entstehen. Die **Abbildung 3** zeigt links eine übliche Kamm-Teststruktur zur Kurzschlußdiagnose und den dazugehörigen Graphen, dessen Kanten nur im Falle entstandener Kurzschlüsse vorhanden sind. Man erkennt, daß die Anzahl der Kanten um eins geringer ist als die Anzahl der Knoten, was bedeutet, daß nur ein vergleichsweise geringer Anteil möglicher Verbindungen (Kanten) tatsächlich realisiert wird.

Abb. 3: Teststrukturen und Graphen

Ziel des 2D-Permutationsverfahrens ist die Realisierung des vollständigen Graphen (Simplex, vgl. Abb. 3 rechts) in einer geometrischen Anordnung, um so alle möglichen (2) Verbindungen zwischen n Anschlußpunkten zur Kurzschlußerkennung einsetzen zu können. Jede dieser Verbindungen darf nur genau einmal vorkommen, um so anhand einer erkannten Kurzschlußverbindung diese innerhalb einer Teststruktur eindeutig lokalisieren zu können.

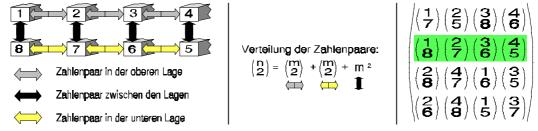

Stehen n Knoten zur Verfügung, so werden diese von eins bis n numeriert und in einer  $(\frac{n}{2},n)$  Matrix angeordnet. Die Elemente dieser 2D-Matrix berechnen sich nach dem in der **Tabelle 1** links angegebenen Algorithmus. Es existiert auch ein konstruktives Verfahren, welches auf die Berechnung der einzelnen Elemente verzichtet [HeWe92]. Die Tabelle 1 zeigt rechts eine 2D-Matrix für 8 Knoten. Man erkennt, daß alle Zahlenpaare zeilenweise verschieden sind. So befindet sich beispielsweise für die Zahl 1 in der Zeile 1 das Zahlenpaar (1,2) in der Zeile 2 die Paare (1,4) und (1,6), in der Zeile 3 die Paare (1,8) und (1,7) sowie in der Zeile 4 schließlich die Paare (1,3) und (1,5). Das 2D-Permutationsverfahren ist allgemeingültig für alle geraden natürlichen Zahlen n mit  $\frac{n}{2} \in \mathbb{N}$  [HeWe92].

$$\begin{bmatrix} j + 2 \cdot i - 2 & \text{für } i, \frac{j}{2} \in \mathbb{N} & \wedge & i \leq \frac{m - j + 2}{2} \\ 2 \cdot m - j - 2 \cdot i + 3 & \text{für } i, \frac{j}{2} \in \mathbb{N} & \wedge & i > \frac{m - j + 2}{2} \\ 2 \cdot i - j - 1 & \text{für } i, \frac{j + 1}{2} \in \mathbb{N} & \wedge & i > \frac{j + 1}{2} \\ j - 2 \cdot i + 2 & \text{für } i, \frac{j + 1}{2} \in \mathbb{N} & \wedge & i \leq \frac{j + 1}{2} \\ a_{i,j} & : 2D\text{-Matrixelemente} & j & : Spaltenindex \\ i & : Zeilenindex & m & : \frac{n}{2} \end{bmatrix}$$

Tab. 1: Algorithmus des 2D-Permutationsverfahrens und 2D-Matrix für n=8

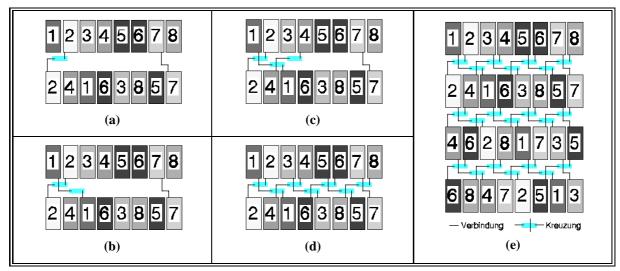

Die Zahlen in der 2D-Matrix werden innerhalb einer Teststruktur in Bahnen umgesetzt, wobei Bahnen mit gleichen Zahlen untereinander leitend verbunden werden müssen. Dieses Verdrahtungsproblem ist mit nur drei Verbindungselementen lösbar, wie die folgende Tabelle zeigt, in der die Zahlen bereits durch Bahnen ersetzt dargestellt sind. Zunächst verbindet man die äußersten Bahnen "2" und "7" mit zwei unterschiedlichen Verbindungselementen (**Tab. 2 (a)**). Anschließend verbindet man die Bahnen "1" (Tab. 2 (b)) mit einem dritten Verbindungselement. Dieses Element wird nun kopiert und horizontal gespiegelt und ergibt so die Verbindung zwischen den Bahnen "4" (Tab. 2 (c)). Diese beiden Elemente werden gemeinsam so oft kopiert, bis alle Verbindungen zwischen den ersten beiden Zeilen hergestellt sind (Tab. 2 (d)). Dieser vollständige Verdrahtungskanal wird nun zwischen alle verbleibenden Zeilen kopiert, was zur vollständigen Lösung des Verdrahtungsproblems führt (Tab. 2 (e)). Dieses Schema ist wiederum für alle geraden natürlichen Zahlen n mit  $\frac{n}{n} \in \mathbb{N}$  anwendbar [HeWe92].

Tab. 2: Verbindungsschema der Elemente innerhalb einer 2D-Matrix

In der in Abbildung 1 rechts beschriebenen Materialanordnung sind neben den möglichen Kurzschlüssen innerhalb einer Lage (zweidimensional (2D)) auch Verbindungen zwischen den Lagen möglich (dreidimensional (3D)), wie dies in der Abbildung 4 links zu sehen ist. Für diese Materialkonfiguration existiert ein 3D-Permutationsverfahren [HeWe92]. Es basiert auf dem 2D-Permutationsverfahren und stellt ebenfalls alle möglichen (<sup>n</sup><sub>2</sub>) Verbindungen zwischen n Anschlußpunkten zur Verfügung. Zwischen den Lagen sind wiederum alle Paare verschieden, innerhalb einer Lage sind alle Paare jeweils doppelt vorhanden (vgl. Abb. 4 mitte), was die Lokalisierung jedoch nicht beeinträchtigt, da diese doppelten Paare in unmittelbarer Nachbarschaft liegen. Die Abbildung 4 zeigt rechts die Anordnung der Zahlen in einer (m,m) 3D-Matrix für n=2·m=8 verschiedene Zahlen.

Abb. 4: Anordnung der Zahlenpaare in einer Materialkonfiguration LEITEND-ISOLIEREND-LEITEND und 3D-Matrix für n=2⋅m=8

#### 5 Karree-Teststrukturen

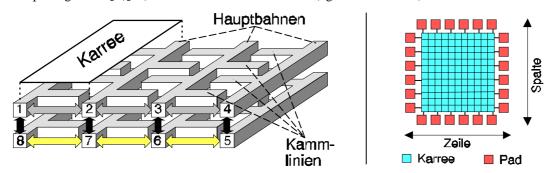

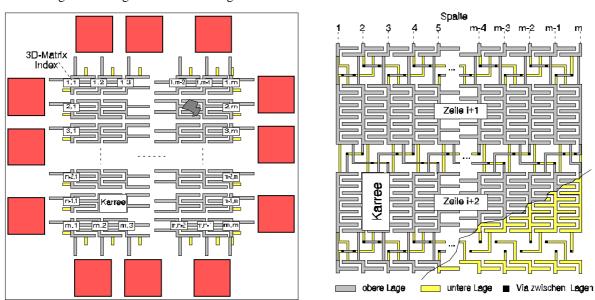

Die 3D-Matrix bzw. die 2D-Matrix läßt sich in Teststrukturen übertragen, in dem die Zahlen in vertikale Hauptbahnen zwischen den Verdrahtungskanälen transformiert werden, so daß zwischen diesen Hauptbahnen rechteckige Felder entstehen. Diese an ein Schachbrett erinnernde Anordnung wird als *Karree-Teststruktur* (KTS) bezeichnet. In diesen Feldern bzw. Karrees werden zur Kurzschlußdiagnose beispielsweise deckungsgleiche oder leicht versetzte horizontale Kammlinien angeordnet, wie dies in der **Abbildung 5 links** zu sehen ist. Bei der Transformation des 2D-Permutationsverfahrens entstehen so innerhalb eines Test-Chips insgesamt  $\frac{n}{2}$ ·(n-1) wohlunterscheidbare Karrees. Bei der Transformation des 3D-Permutationsverfahrens entstehen innerhalb eines Test-Chips insgesamt  $\frac{n}{2}$ ·( $\frac{n}{2}$ -1) wohlunterscheidbare Karrees (vgl. Abb. 5 rechts).

Abb. 5: Hauptbahnen und Kammlinien der Karree-Teststruktur und Anordnung der KTS in einem Test-Chip

Durch die flexible Größe der Karrees entwirft man je Anschlußpunktkonfiguration einmalig die vertikalen Hauptbahnen (Karree-Begrenzung) sowie die Verdrahtungskanäle und die Anbindung an die Anschlußpunkte (siehe Abb. 6 links). Diese Anbindung ist trivial, da alle verschiedenen Zahlen ("Spannungen") mindestens einmal am Rand der Matrizen vorkommen (siehe Abb. 4 rechts und Tab. 1). Bei der Verbindung der Zahlen (Bahnen) in der 3D-Matrix sind die Verdrahtungskanäle ebenfalls gleich, allerdings muß hier zusätzlich eine Lagentransformation durchgeführt werden (siehe Abb. 6 rechts). Innerhalb der Karrees können je nach gegebenen Entwurfsregeln beliebige Kammlinien eingesetzt werden.

Abb. 6: Pad-Anbindung der Karree-Teststruktur und Verdrahtungskanäle

Wenn ein Defekt zu einem Kurzschluß zwischen zwei Leitungen führt, kann aus den Nummern der Anschlußpunkte, zwischen denen ein sprunghaft geringerer Widerstand gemessen wird, auf die Defektart und die Position des Defekts geschlossen werden (Algorithmen siehe [HeWe92]).

# 6 Datenanalyse

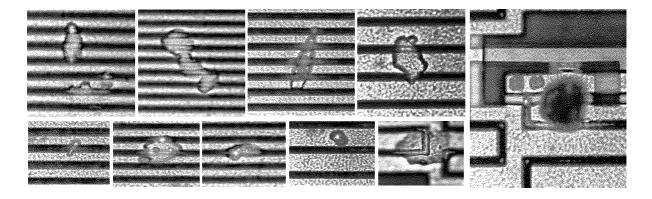

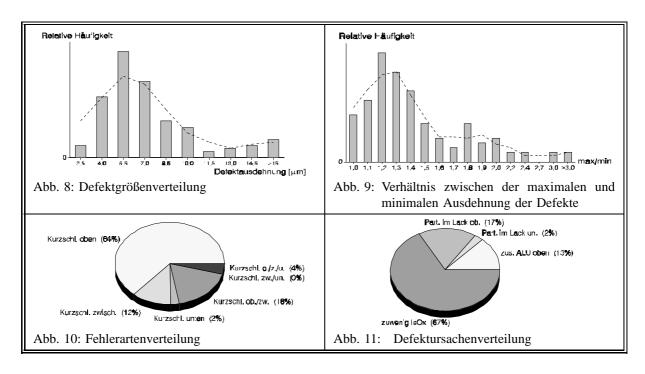

Am *Institut für Mikroelektronik Stuttgart* (**IMS**) sind diverse Karree-Teststrukturen gefertigt worden. Die Test-Chips enthalten 870 Karrees, deren Kammlinien zum Teil deutlich unter den gültigen Entwurfsregeln des IMS liegen. Alle Prozeßschritte entstammen dem IMS 2 µm CMOS Backend Process. Die Lithographieschritte sind mit einem Elektronenstrahl-Direktschreibeverfahren durchgeführt worden. Die deutlich unterhalb der gültigen Entwurfsregeln liegenden Abmessungen der Teststrukturen können zu einer über dem Durchschnitt liegenden Defektdichte führen, was in diesem Fall eine bessere Kontrolle des Verfahrens zur Lokalisierung der Defekte ermöglicht. Zum Test ist ein Digitaltester HP82000 eingesetzt worden. Nach der Lokalisierung der Defekte erfolgte eine optische Nachuntersuchung zur Bestimmung der Defektgrößen, -formen und -ursachen. Die **Abbildungen 7 bis 11** geben einen Überblick über die so erhaltenen Daten.

Abb. 7: Diagnostizierte Defekte innerhalb von Karree-Teststrukturen

# 7 Zusammenfassung und Ausblick

Außer den in diesem Beitrag beschriebenen Karree-Teststrukturen zur Kurzschlußdiagnose stehen weitere Karree-Teststrukturen zur Verfügung, um auch Defektarten zu untersuchen, die zu Unterbrechungen führen können. Die Verwendung von Karree-Teststrukturen bietet prinzipiell folgende Vorteile:

- Die Karree-Teststrukturen sind in verschiedenen Materialkonfigurationen zur Diagnose topologischer Defekte einsetzbar.

- Die Karree-Teststrukturen sind bezüglich verschiedener Entwurfsregeln (Design Rules) leicht skalierbar und modular zum Einbau in Test-Chip einsetzbar, wobei die gleiche Randanschlußpunktkonfiguration der Standard-Chips verwendet wird (boundary pads).

- Ein Test-Chip wird mit den gleichen Meßapparaturen untersucht wie ein Standard-Chip, damit keine spürbaren Verzögerungen der laufenden Fertigung auftreten.

- Die Datenanalyse ermöglicht eine hohe Selektivität bezüglich der Defektarten, um innerhalb des gesamten Prozesses die Güte einzelner Prozeßschritte bestimmen zu können.

- Auch zufällige Defekte werden dank der großen defektsensitiven Fläche zuverlässig entdeckt.

- Optische Untersuchungen werden durch die Lokalisierung der Defekte anhand der Daten der vorherigen elektrische Messungen deutlich beschleunigt.

#### 8 Literatur

- [BCKJ91] Bruls, E. M. J. G., Camerik, F., Kretschman, H. J., Jess, J. A. G. A; Generic Method to Develop A Defect Monitoring System for IC Processes; International Test Conference, 1991

- [Bueh83] Buehler, M. G.; Microelectronic Test Cips for VLSI Elektronics; VLSI Electronics Microstructure Sience, Vol 9, Chap.9, Academic Press, 1983

- [Ferr85] Ferris Prabhu, A. V.; Defect Size Variations and Their Effect on the Critical Area of VLSI Devices; IEEE Journal of Solid-State Circuits, Vol. SC-20, No. 4, August 1985

- [FeSh88] Ferguson, F. J., Shen, J. P.; Extraction and Simulation of Realistic CMOS Faults using Inductive Fault Analysis; International Test Conference, 1988

- [HeWe92a] Hess, C., Weiland, L. H.; Test Structure for the Detection, Localization, and Identification of Short Circuits with a High Speed Digital Tester; International Conference on Microelectronic Test Structures, San Diego, March 1992

- [HeWe92] Hess, C., Weiland, L. H.; Teststrukturen zur Bestimmung von Defektparametern für hochintegrierten Schaltungen; Diplomarbeit am Institut für Rechnerentwurf und Fehlertoleranz, Universität Karlsruhe, Feb. 1992

- [LYWM86] Lukaszek, W., Yarbrough, W., Walker, T., Meindl J.; CMOS Test Chip Design for Process Problem Debugging and Yield Prediction Experiments; Solid State Technology, March 1986

- [Spie93] Spiegel, G.; Optimized Test Cost Using Fault Probabilities; to appear in ETC 93, Paris, April 1993

- [SpSt92] Spiegel, G., Stern, O.; Repräsentation und Analyse realistischer Fehlfunktionen in hochintegrierten Schaltungen; 4. ITG/GI-Workshop, Bad Kissingen, März 1992

- [Stap84] Stapper, C. H.; Modeling of Defects in Integrated Circuits Photolithographic Patterns; IBM J. Res. Develop., July 1984